#### **Final Assessment**

### **Md Bakhtiar Chowdhury**

ID: 2121210061

**Department: CSE**

Semester: Fall 2023

Batch: 21<sup>th</sup>

Course Title: Digital Electronics & Pules

**Technique**

**Course Code: CSE 223**

### **Submitted To:**

Md. Shahin Khan

Lecturer, Dept. of CSE/CSIT

Victoria University of Bangladesh

Submission Date: 07 February, 2023

### Answer to the question No 1(g)

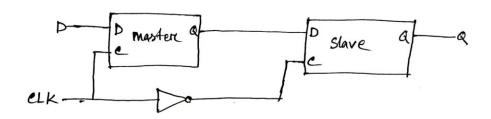

1.a) Answer: - master slave Flip flop is a type of clocked flip flop consisting of master and slave elements that are clocked on complementary teams fettion of the clock signal.

master-slave Flip Flops.

- The circuits sample the D input and changes its output of the negative edge of the clock, clk.

- when the eleck is 0, the output of the interreter is 1. The slave latch is enabled and its output a is equal to the master output y. The master latch is disabled (CLK=0)

- when the  $\infty$  CLK changes to high D input is transferred to the master latch: the slave remains disable as long as CLK is low. amy change in the input changes y. But not a. the output of the flip-flop can change when CLK makes a transition  $1 \to 0$ .

### ID- 2121210061, Name: Md Bakhtiar Chowdhury, Program: BSc in CSE (R)

#### Course Code: CSE 223, Course Title: Digital Electronics & Pules Technique

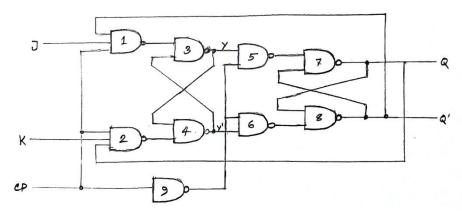

1.b) Draw masher and describe the masher-slave FUP-FLOP using JK

#### describe:-

- \* TWO JK-Flip-Flops: Labeled . Master and "slave" in the

- \* clock signal (cp): Represented by a square wave symble on the left.

- \* inverted clock signal (ep): created by the inverter (not orde) below the elock signal and connected to the slave Flip flop

- \* J & K inputs: shared by both flip-flops, controlling their next state.

- \* am and as outputs: outputs of the master and slave Flip Hors.

Funetionality: - master operation during positive clock edge (CP High)

- Jand K inputes defermine the next state of the master flip flop.

- · slave Flip-flop is isolated

slave operation during negative clock edge (cplow)

- · master flip flop output becomes the new data for the glave flip-flop

- · slave . flip-flop captures this data, updating its as output

- · marsher flip flop is isolated (cp High)

Answer to the question NO 2(a)

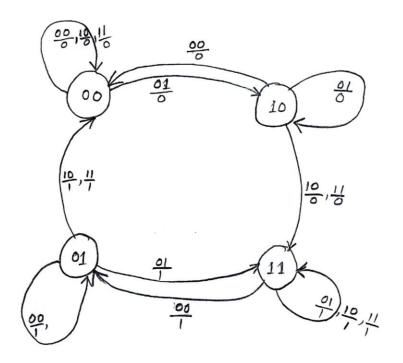

20) Answert: Draw the state diagram for the given Auble.

output depends on state.

Next State depends on input and current state

### Answer to the guestion NO 3(A)

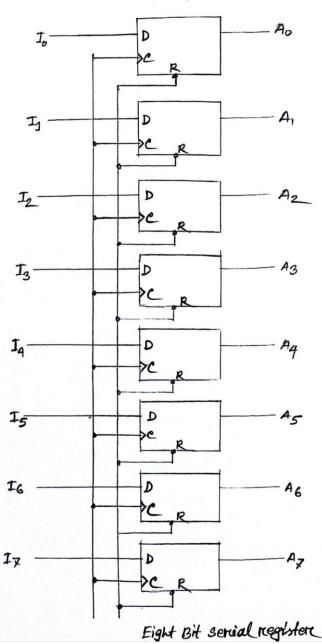

3.a) Answer: An 8 bit servial register is a type of data storage element that stories binary information in a sequential marmer. It is often used in digital system for tusks such as data transmission, shift operation, temporary store data

- is a binary storage element capable of storage one bit of data.

in this case. There are eight this floor laboled Do through Dz callectively to forming an 8 bit negesters.

- Beruial Data flow: The armows indicate the flow of data in a Beruial mammen. data is shifted from one flip-flop to the next sequentially. This means that each eleck cycle on shift operation.

- B) shift negesten operation; the serial to negester is offen used as a sift negesten. serial data is loded into the first thip-flop (Do) and subsequent clock pulse shift the data to the night.

- elock input: The shift of data from one flip-flop to the next is controlled by a clock signal. each rising on beling edge of the clock thinggens the shift operation.

- B parallel output: although the data is shifted servially. the poralle outputs (Ac to Ax) can be used to read the entired content of the neglister simultaneously.

### Answer to the question NO 3 (b)

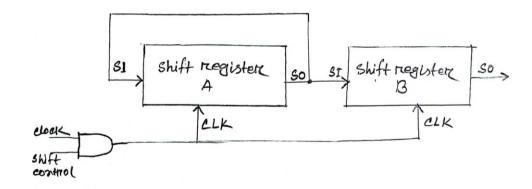

- 3.b. Answer: There are two main ways to achieve social transfer frurom Register A to B.

- (1) Using a shift register: this method involves connecting the serial output (50) of register A to the serial input (51) of a shift register. Then connect the clock signal of both register together. With each clock pulse, the data from A will be shifted into the first bit of the glift register and simultaneously all other bits within the shift register will more one position to the right, after N clock pulse. The entire data from A will be present in the shift register ond finally connecting the so of the shift register to the SI of register B and providing another N clock pulse will transfer the data from the shift register to register B.

- D using dedicated controller: this method is more complex but offers greater flexibility. You can use a microcontroller or any programmable logic device to control the triansfer process. The controller can read data from register a one bit of a time and then write it to register B. shift the existing data within B one position to the right each data write

Here some additional consideration for the servial transfer.

- · clock synchronization.

- · pata format.

- · Ennon Metection/connection.

- · Handwar nesources.

#### ID- 2121210061, Name: Md Bakhtiar Chowdhury, Program: BSc in CSE (R)

#### Course Code: CSE 223, Course Title: Digital Electronics & Pules Technique

Answer to the question NO 4(a)

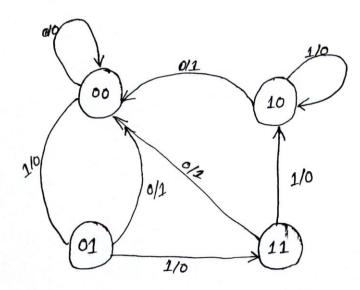

4.a) Dreaw the state diagram for the table

state terble

A(++1)=Ax+Bx B(++1)=A'x Y=(A+B)x'

| present state |   |          |          |          |          |  |

|---------------|---|----------|----------|----------|----------|--|

| A             | В | ½=0<br>Α | x=1<br>B | x=0<br>y | x=1<br>y |  |

| 0             | o | o        | 0        | 0        | 0        |  |

| Ø             | 1 | 0        | 1        | 1        | 0        |  |

| 1             | 0 | 0        | 1        | 1        | 0        |  |

| 1             | 1 | 0        | 1        | 1        | 0        |  |

#### 1 state diagram

>>>>END<