# Mid Assessment | Fall - 2023

Md. Shafayet Hossain

CSE - 21<sup>st</sup> Batch | Course Code: CSE - 223

Course Title: Digital Electronics & Pulse Technique

**ID:** 2121210071

# Answer to the Question no-1

# <u>(a)</u>

## Flip-flop

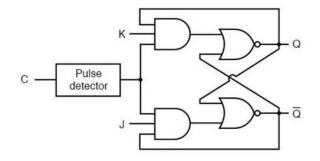

Flip-flop is a circuit that maintains a state until directed by input to change the state. A basic flip-flop can be constructed using four-NAND or four-NOR gates. Flip flop is popularly known as the basic digital memory circuit. It has its two states as logic 1(High) and logic 0(low) states.

The most commonly used type of flip-flop is the simple SR version. This design inputs a signal as either S (SET) or R (RESET). This type of circuit outputs "1" when it receives an "S" input, and outputs "0" as the result of an "R" input. Once the outputs have been generated, they are stored as stable one-bit data in the bi-stable vibrator until the circuit is turned off.

A gated SR latch circuit allows use of both the memory and a time counter.

## <u>(b)</u>

## Types of Sequential Circuits:

There are two main types of sequential circuits: (a) Synchronous and (b) Asynchronous.

### (a) Asynchronous Sequential circuits -

Asynchronous circuits do not synchronize with positive edge or negative edge of the clock signal, that means, the outputs of asynchronous sequential circuits do not change or affect at the same time and change their state immediately when there is a change in the input signal.

### (b) Synchronous Sequential circuits -

Synchronous circuits synchronize with either positive edge or negative edge of the clock signal, which means, the outputs of synchronous sequential circuits change or affect at the same time.

# Answer to the Question no- 3

# <u>(a)</u>

#### Mealy model

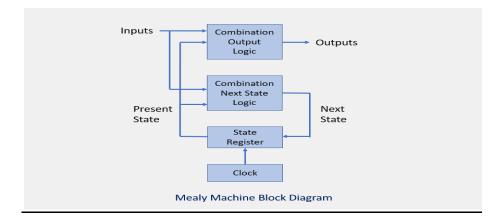

A Mealy model is a state machine where the outputs depend on both the current state and the inputs. This means that the outputs can change as soon as the inputs change, without waiting for a clock signal or a state transition. A Mealy model can have fewer states and faster response than a Moore model, but it may also have more glitches and hazards due to the asynchronous outputs.

#### Moore model

A Moore model is a state machine where the outputs depend only on the current state, not on the inputs. This means that the outputs change only when the state changes, which is usually triggered by a clock signal or a specific input combination. A Moore model can have more states and slower response than a Mealy model, but it may also have less glitches and hazards due to the synchronous outputs.

## <u>(b)</u>

A Mealy Machine is an FSM whose output depends on the present state as well as the present input. It can be described by a 6 tuple (Q,  $\Sigma$ , O,  $\delta$ , X, q<sub>0</sub>) where –

- **Q** is a finite set of states.

- $\Sigma$  is a finite set of symbols called the input alphabet.

- **O** is a finite set of symbols called the output alphabet.

- $\boldsymbol{\delta}$  is the input transition function where  $\delta: Q \times \Sigma \rightarrow Q$

- **X** is the output transition function where  $X: Q \times \Sigma \rightarrow O$

- $q_0$  is the initial state from where any input is processed ( $q_0 \in Q$ ).

# <u>(c)</u>

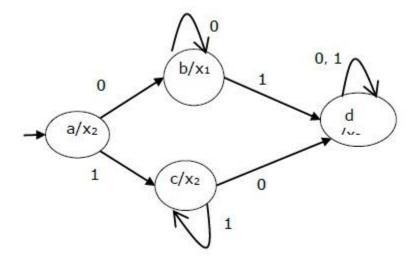

Moore machine is an FSM whose outputs depend on only the present state.

A Moore machine can be described by a 6 tuple (Q,  $\Sigma$ , O,  $\delta$ , X, q<sub>0</sub>) where –

- **Q** is a finite set of states.

- **Σ** is a finite set of symbols called the input alphabet.

- **O** is a finite set of symbols called the output alphabet.

- **\delta** is the input transition function where  $\delta: Q \times \Sigma \rightarrow Q$

- **X** is the output transition function where X:  $Q \rightarrow O$

- $q_0$  is the initial state from where any input is processed ( $q_0 \in Q$ ).

### State Diagram of Moore Machine-

# Answer to the Question no- 4

# <u>(a)</u>

The design procedure in electronics involves creating circuits and systems to achieve specific functionality. Here are some basic principles for the design procedure in electronics-

| Define Specifications | <ul> <li>Testing and Debugging</li> </ul>      |

|-----------------------|------------------------------------------------|

| Research Components   | <ul> <li>Compliance and Standards</li> </ul>   |

| Schematic Design      | Documentation                                  |

| Component Selection   | Iterative Design                               |

| Simulation            | Power Considerations                           |

| Layout Design         | <ul> <li>Reliability and Robustness</li> </ul> |

| Prototyping           | Cost Optimization                              |

|                       |                                                |

# <u>(b)</u>

#### Register

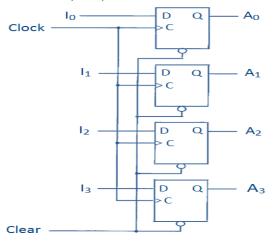

Registers are data storage devices that are more sophisticated than latches. A register is a group of binary cells suitable for holding binary information, cascaded flip-flops used to store related bits of information is known as a register.

### **Circuit of 4-bit register:**

Various types of registers are available commercially. The simplest register is one that consists only of flip-flops, with no external gates. The 4-bit register circuit diagram shows that such a register is constructed with four D flip-flops.

Fig: 4-bit Register

The common clock input triggers all flip-flops on the rising edge of each pulse, and the binary data available at the four inputs are transferred into the 4-bit register. The four outputs can be sampled at any time to obtain the binary information stored in the register. The clear input goes to a special terminal in each flip-flop. When this input goes to 0, all flip-flops are reset asynchronously. The clear input is useful for clearing the register to all O's before its clocked operation. The clear input must be maintained at logic 1 during normal clocked operation.

# <u>(c)</u>

#### **Block Diagram of Decade Counter**

The block diagram of the decade counter is shown below.

The BCD counter or decade counter has 4 jk flip flops with 16 combinational states as shown in the figure above. Out of 16 states, 10 are used. When the counters are connected in series, we can count up to 100 or 1000 based on the application.