Victoria University of Bangladesh Name: Md. Ziaul Hoque "Sohel" Student ID: 2221220031 Course Title: Digital Electronics and Pulse Technique Course Code: CSE-223 Batch: 22<sup>nd</sup> (evening) Semester: Fall-2023

## Ans to the Que No 1(A)

## Filip Flop:

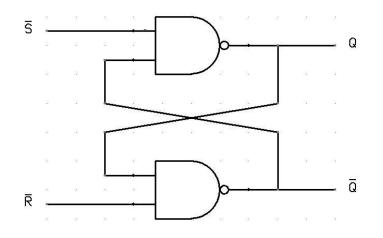

A flip flop in digital electronics is a circuit with two stable states that can be used to store binary data. The stored data can be changed by applying varying inputs. Flip-flops and latches are fundamental building blocks of digital electronics systems used in computers, communications, and many other types of systems. Both are used as data storage elements.

example, let us talk about SR latch and SR flip-flops. In this circuit when you Set S as active, the output Q will be high and Q' will be Low. This is irrespective of anything else. (This is an active-low circuit; so active here means low, but for an active high circuit, active would mean high) A flip-flop, on the other hand, is a synchronous Circuit and is also known as a gated or clocked SR latch.

## Ans to the Que No 1(B)

#### Types of Sequential Circuits:

The sequential circuits are classified into two types

- Synchronous Circuit

- Asynchronous Circuit

In synchronous sequential circuits, the state of the device changes at discrete times in response to a clock signal. In asynchronous circuits, the state of the device changes in response to changing inputs.

#### Synchronous Circuits:

In synchronous circuits, the inputs are pulses with certain restrictions on pulse width and propagation delay. Thus, synchronous circuits can be divided into clocked and un-clocked or pulsed sequential circuits.

#### Asynchronous Circuits:

An asynchronous circuit does not have a clock signal to synchronize its internal changes of the state. Hence the state change occurs in direct response to changes that occur in primary input lines. An asynchronous circuit does not require precise timing control from <u>flip-flops</u>. Asynchronous logic is more difficult to design and it has some problems compared to synchronous logic. The main problem is that the digital memory is sensitive to the order that their input signals arrive them, like, if two signals arrive at a flip-flop at the same time, which state the circuit goes into can depend on which signal gets to the logic gate first.

## Ans to the Que No 2 (A)

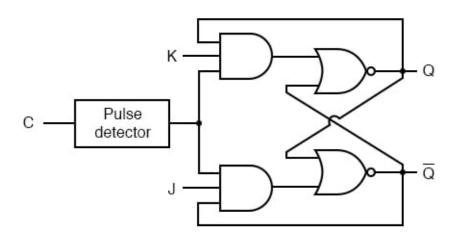

JK Flip-Flop:

| С | J | к | Q      | Q      |

|---|---|---|--------|--------|

| Г | 0 | 0 | latch  | latch  |

| Г | 0 | 1 | 0      | 1      |

| Г | 1 | 0 | 1      | 0      |

| Г | 1 | 1 | toggle | toggle |

| х | 0 | 0 | latch  | latch  |

| х | 0 | 1 | latch  | latch  |

| х | 1 | 0 | latch  | latch  |

| х | 1 | 1 | latch  | latch  |

Ans to the Que No 2 (A)

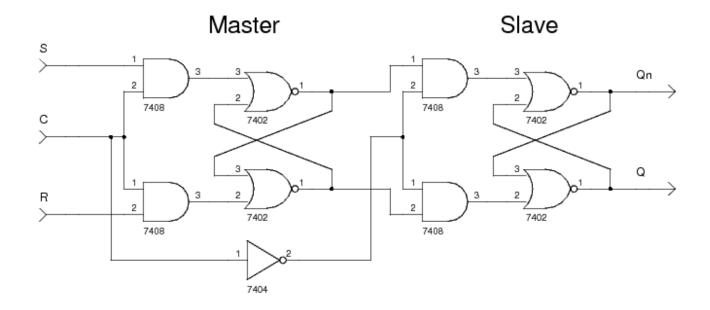

Master Slave SR Flip Flop:

## Ans to the Que No 3 (A)

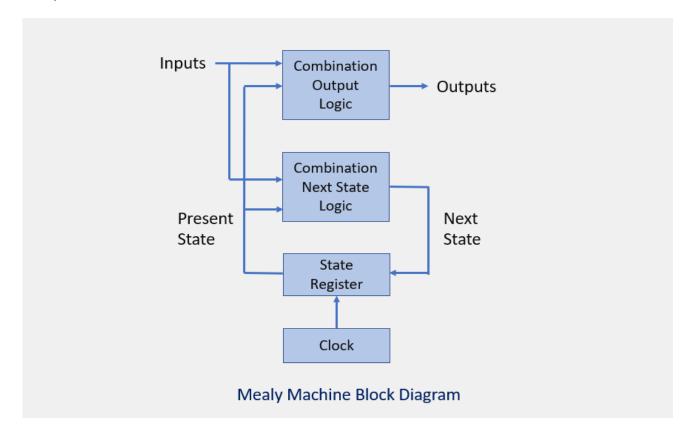

### Mealy model:

A Mealy model is a state machine where the outputs depend on both the current state and the inputs. This means that the outputs can change as soon as the inputs change, without waiting for a clock signal or a state transition. A Mealy model can have fewer states and faster response than a Moore model, but it may also have more glitches and hazards due to the asynchronous outputs. A Mealy model is often preferred for applications that require fast and complex output reactions.

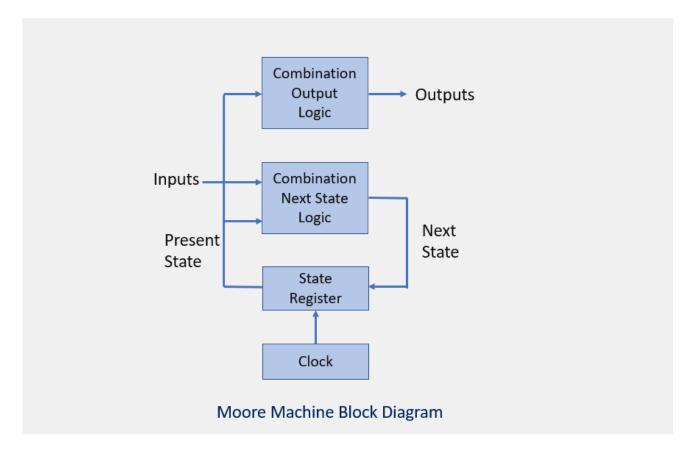

#### Moore model:

A Moore model is a state machine where the outputs depend only on the current state, not on the inputs. This means that the outputs change only when the state changes, which is usually triggered by a clock signal or a specific input combination. A Moore model can have more states and slower response than a Mealy model, but it may also have less glitches and hazards due to the synchronous outputs. A Moore model is often preferred for applications that require stable and simple output actions.

# Ans to the Que No 3 (B)

## Mealy state machine:

## Ans to the Que No 3 (C)

## Moore state machine:

- END -