Victoria University of Bangladoch Department computer Science & Engineering Name: Ashit Kumar Student 10: 2221220011. Programs B. Sc in asE Semister: Fall-2022 Batch: 22nd (Evening) Course code: CSE-413. Course Title: Microprocessore & Interfacing Mid-terron dissessment

Scanned By Camera Scanner

Future of microprocesson:

- D'Amhitestere: Mieroprocessors are available is 8 bit, 16 bit 32 bit, 64 bit anchitectures. The bit sizes can also be called bus with.

- Departured processing: The matticent this that conterns more their one processon in it, aneibles puralled processing at independent pontions of a forsk.

- @ Matti processing and time searing: The time is devided in to several ego! slices and it is allated to various processing is a notendtobin turbion.

- 1 Caregonies of micro processing;

- @fedroed Instaction set Computer

- Decompten Instruction set computer

- @ special purpose processory.

#### Ans to the gens NO I (B)

Bit menipulation instructions sets (BMI sets)

are cretensions to the ×86 instruction set anchitecture for microprocession trom intel and Amo. The purpose of these instruction sets is to improve the speed of the manipulation. All the instruction the speed of the manipulation and openate only in these sets are non-simo and openate only in these sets are non-simo and openate only in general-purpose are gioters.

There are two sets published by Intul: BMI and BMI 2: they were both Introduced with the ftos well mercouron teetwee with BMI1 matering well mercouron teetwee with BMI1 matering well mercouron teetwee with BMI1 matering well entered by AMD s ABM instruction set and teatwees of eretending them. Anothere two sets were BMI2 cretending them. About the Bit marpulation published by AMD. ABM (Advonced Bit marpulation published by AMD. ABM (Advonced Bit marpulation which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by which is also a subset of SSF 4a implemented by

Scanned By Camera Scanner

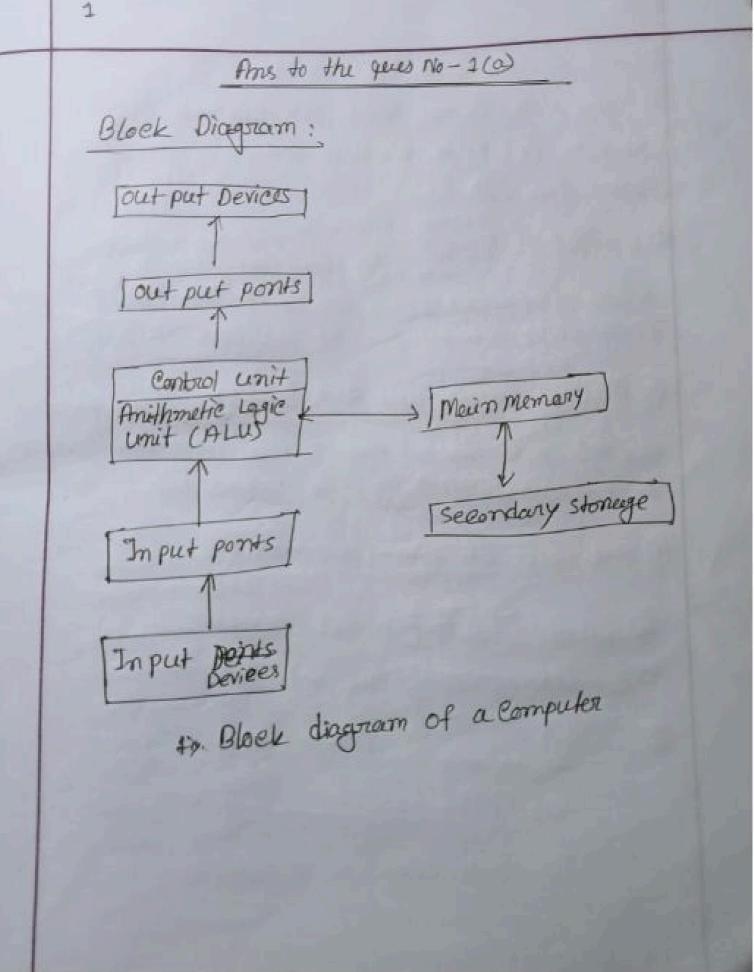

#### Ams to the fue No-2(a)

Initially when any device has to send dute between the device and the memory, the between hers to seid DMA suggest to DMA Contrater. The DMA Controller Senets - Hold neglest to the epu and waits for the epu to assert the HLDA.

# Ans to the ques No-26)

#### teatures to 8257:

- (a) It heat four chemnels which can be used over four Ito devices.

- (b) Each charmel has 16 bit admess and 14 bit ranker

- @ Each channel can trunsfer duter up to 64 KLit

- @ Even channel can be programmed independently.

- @ Eeach charmel can perfor m need transfor write transfer and verity transfer operations.

- 1) It generates MARK signal to the peripheral device that 128 by tesnave been transferred

- DI+ regimes a single phose clock.

- (1) Itis freghency flores from 20042 to 3MHz

Scanned By Camera Scanner